Bài viết này trình bày về một thiết kế điều khiển truy xuất bộ nhớ EEPROM theo giao thức đọc ghi nối tiếp. lõi IP có giao tiếp với bus hệ thống APB. Bộ nhớ EEPROM là AT93C46 của hãng Atmel.

Nội dung bài 1 giới thiệu về bộ nhớ AT93C46, giao thức APB và phân tích tổng quan lõi IP sẽ thiết kế.

Nội dung bài 1 giới thiệu về bộ nhớ AT93C46, giao thức APB và phân tích tổng quan lõi IP sẽ thiết kế.

1. Tổng quan về bộ nhớ EEPROM AT93C46

AT93C646 là loại bộ nhớ EEPROM có thể lập trình được. Bộ nhớ có dung lượng 1024 bit:

- 64 word, mỗi word 16 bit khi chân ORG nối đến VCC

- 128 word, mỗi word 8 bit khi chân ORG nối đến GROUND

Giao tiếp của bộ nhớ là loại nối tiếp với các chân đơn giản như sau:

|

| Hình 1. Các chân của bộ nhớ EEPROM AT93C46 |

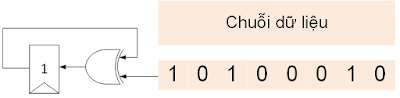

Nguyên tắc truy xuất của AT93C46 là "một lệnh hợp lệnh bắt đầu được phát cùng lúc với cạnh lên của chân CS". Một lệnh bắt đầu với 1 bit START, theo sau là mã lệnh và địa chỉ ô nhớ.

Các lệnh mà bộ nhớ EEPROM hỗ trợ gồm:

- READ: Lệnh đọc chứa địa chỉ ô nhớ sẽ đọc. Sau khi nhận lệnh đọc, địa chỉ sẽ được giải mã mà dữ liệu ô nhớ được dịch từng bit ra chân DO. Đầu tiên, 1 bit 0 sẽ được dịch ra trên DO. Sau đó, bit MSB, D15 hoặc D7, được dịch ra trên DO. Dữ liệu ở chân DO được dịch ra theo cạnh lên SK.

- EWEN: Lệnh cho phép chế độ xóa hoặc ghi bộ nhớ. Khi cấp nguồn cho bộ nhớ, chế độ cho phép xóa hoặc ghi sẽ mặc định bị tắt để đảm bảo tính toàn vẹn của dữ liệu. Lệnh này phải được phát trước khi sử dụng lệnh xóa hoặc ghi bộ nhớ. Chú ý, bộ nhớ chỉ thoát khỏi trạng thái cho phép xóa hoặc ghi khi lệnh tắt chế độ xóa/ghi được phát hoặc bộ nhớ bị ngắt nguồn.

- ERASE: Lệnh xóa tất cả các bit của một ô nhớ về "1". Sau khi nhận được lệnh xóa, bộ nhớ sẽ bắt đầu thực hiện quá trình xóa. Để kiểm tra trạng thái xóa bộ nhớ, chân CS sẽ được kéo xuống mức thấp trong it nhất 250 ns sau khi phát lệnh xóa, sau đó CS sẽ tích cực mức "1" và kiểm tra giá trị logic trên DO. Nếu DO = 1 thì EEPROM đã xóa xong và một lệnh mới có thể được phát.

- WRITE: Lệnh ghi tất cả các bit của một ô nhớ. Sau khi bit dữ liệu cuối cùng được dịch vào EEPROM trên DI, bộ nhớ bắt đầu vào trạng thái ghi. Tương tự lệnh xóa, việc ghi bộ nhớ cần một khoảng thời gian để thực hiện. Sau khi ghi, chân CS phải được kéo xuống mức thấp ít nhất trong 250 ns, sau đó kéo lên lại mức "1" và kiểm tra trạng thái DO. Nếu DO = 0, quá trình ghi chưa hoàn thành. Nếu DO = 1, quá trình ghi đã hoàn thành.

- ERAL: Xóa tất cả các bit của bộ nhớ về 1. Kiểm tra trạng thái xóa tương tự lệnh xóa.

- WRAL: lệnh ghi tất cả các bit của bộ nhớ. Kiểm tra trạng thái xóa tương tự lệnh ghi.

- EWDS: Lệnh tắt chế độ lập trình (xóa/ghi) của bộ nhớ

|

| Hình 2. Bảng mã lệnh của AT93C46 |

Để thiết kế được bộ điều khiển bộ nhớ EEPROM, một phần quan trọng cần quan tâm là timing của các tín hiệu giao tiếp.

|

| Hình 3. Định thời giao tiếp của bộ nhớ AT93C46 |

Các bạn xem thêm datasheet để biết chi tiết các thông số trên. Ở đây, một số ý chính sẽ được tóm lược:

- Tùy vào điện áp cấp cho AT93C46 mà timing của các tín hiệu sẽ có giới hạn khác nhau. Ví dụ, với tầm điện áp từ 4.5V đến 5.5V, tần số xung SK tối đa là 2 Mhz tương ứng chu kỳ 0.5 us = 500 ns. Nếu sử dụng điện áp từ 2.7V đến dưới 4.5V thì điện áp tối đa chỉ 1 Mhz tương ứng chu kỳ 1 us = 1000 ns. Nếu sử dụng điện áp từ 1.8V đến dưới 2.7V, tần số xung SK tối đa là 0.25 Mhz tương ứng chu kỳ 4 us = 4000 ns

- Tất cả các chỉ số timing được liệt kê phải được đảm bảo. So sánh với datasheet thì các giá trị timing phải đảm bảo lớn hơn hoặc bằng giá trị MIN và nhỏ hơn hoặc bằng giá trị MAX

|

| Hình 4. Bảng các thông số timing của EEPROM |

2. Giao tiếp APB - AMBA 2.0

Giao tiếp APB (Advanced Peripheral Bus) là một trong bộ giao tiếp AMBA (Advanced Microcontroller Bus Architecture). AMBA là một cấu trúc bus hệ thống sử dụng trong các vi điều khiển được phát triển bởi ARM. AMBA có nhiều cấu trúc bus khác nhau như AXI, AHB, ASB, APB. Trong đó, APB là bus dùng để giao tiếp với các ngoại vi không đòi hỏi tốc độ xử lý nhanh như UART, SPI, I2C, ...

APB có giao tiếp đơn giản gồm các tín hiệu như sau:

- PCLK: Tín hiệu clock đồng bộ hoạt động theo cạnh lên

- PADDR: địa chỉ thanh ghi được truy xuất

- PWRITE: tín hiệu cho phép ghi

- PSEL: tín hiệu cho phép

- PENABLE: tín hiệu báo pha ENABLE của một truy xuất đọc hoặc ghi

- PWDATA: dữ liệu ghi

- PRDATA: dữ liệu đọc

|

| Hình 5. Giao tiếp APB - Ghi (trái) và Đọc (phải) |

Master APB: thành phần lái các tín hiệu điều khiển của bus APB. Master APB thường là một bus khác có tốc độ cao hơn trong hệ thống bus, ví dụ như AXI, AHB, ... tuy nhiên nó cũng có thể là một master đầu cuối có giao tiếp trực tiếp đến bus APB.

Slave APB: thành phần nhận các tín hiệu điều khiển của bus APB. Bộ điều khiển EEPROM trong bài này là một slave APB

|

| Hình 6. Minh họa về kết nối của APB bus |

Hình minh họa sau đây là một ví dụ về kết nối bus hệ thống. Trong đó, master APB là DMA-230 và bus AHB.

|

| Hình 7. Minh họa một kết nối bus hệ thống trong vi điều khiển (https://developer.arm.com) |

Hoạt động của giao tiếp APB đơn giản gồm 3 pha (trạng thái):

- IDLE: khi PSEL = 0. Lúc này, PENABLE cũng phải bằng "0" và slave APB không quan tâm đến giá trị các tín hiệu điều khiển còn lại trên bus như PWRITE, PWDATA hay PADDR

- SETUP: khi PSEL = 1 và PENABLE = 0. Lúc này, các tín hiệu điều khiển trên bus phải có giá trị hợp lệ. Cá tín hiệu điều khiển bao gồm PADDR, PWRITE và PWDATA nếu là một truy cập "ghi".

- ENABLE: khi PSEL = 1 và PENABLE = 0. Lúc này, slave APB phải nhận xong các giá điều khiển và phải lái PRDATA đến giá trị hợp lệ nếu đó là một truy cập "đọc"

Chú ý, mỗi truy cập "đọc" hoặc "ghi" từ master APB đến slave APB phải qua 2 bước là SETUP và ENABLE. Sau bước ENABLE nếu không có truy cập nào khác thì trạng thái truy cập sẽ về IDLE nhưng nếu master APB tiếp tục có truy cập tiếp theo thì có thể lái trực tiếp qua trạng thái SETUP.

|

| Hình 8. Các trạng thái hoạt động của bus APB |

3. Phân tích tổng quan lõi IP truy xuất bộ nhớ

Bộ điều khiển truy xuất bộ nhớ sẽ có những đặc điểm chính sau:

- Giao tiếp bus APB - AMBA 2.0 trong hệ thống bus 32-bit

- Cho phép cấu hình timing giao tiếp bộ nhớ

- Giao tiếp với EEPROM thông qua 5 chân ORG, CS, SK, DI và DO

|

| Hình 9. Sơ đồ tín hiệu giao tiếp của lõi IP APB_EEPROM_CTRL |

Để thiết kế bộ điều khiển truy xuất bộ nhớ, phần quan trọng nhất là phân tích các yêu cầu về timing bộ điều khiển sao cho đáp ứng yêu cầu trong datasheet.

Tần số fSK:

Thiết kế sử dụng clock đồng bộ pclk. Để tạo ra xung SK phù hợp, một thanh ghi sẽ được sử dụng cho phép thiết lập hệ số để chia clock pclk thành xung SK với duty cycle là 50%, nghĩa là độ rộng mức cao và mức thấp trong 1 chu kỳ SK bằng nhau. Bạn có thể chọn duty cycle khác nhưng việc chọn duty cycle 50% giúp cho việc thiết kế bộ chia clock đơn giản hơn.

Độ rộng mức cao (fSKH) và độ rộng mức thấp (fSKL):

Vì chúng ta sẽ thiết kế tạo xung SK có duty cycle là 50% nên chỉ cần chu kỳ fSK thỏa mãn là 2 thông số này thỏa mãn. Ví dụ, ở điều kiện 4.5V <= Vcc <= 5.5V, tần số fSK được thiết lập tối đa là 2 Mhz thì chu kỳ là 500 ns. Vì duty cycle là 50% nên, mỗi chu kỳ SK có 250 ns mức "1" và 250 ns mức "0" và thỏa mãn yêu cầu về độ rộng fSKH và fSKL.

Thời gian giữa cạnh lên CS và cạnh lên đầu tiên của SK (tCSS):

Trường hợp xấu nhất, tCSS tối thiếu bằng 200 ns nên một nửa xung SK sẽ được dùng để tạo độ trễ này. Một nữa xung SK, cho trường hợp nhanh nhất bằng 250ns khi fSK = 2 Mhz sẽ luôn thỏa mãn yêu cầu và giúp thiết kế đơn giản hơn.

Thời gian giữa cạnh xuống xung SK cuối cùng và cạnh xuống của CS (tCSH):

Độ trễ yêu cầu là 0 ns, tức là không cần trễ. Nếu trong thiết kế, chúng ta cho CS xuống cùng với cạnh xuống SK thì cạnh xuống CS tại chân EEPROM có thể xuất hiện trước cạnh xuống xung SK vì độ trễ của SK khi kết nối từ bộ điều khiển đến EEPROM có thể lớn hơn độ trễ của CS. Để tránh điều này, thiết kế sẽ sẽ điều khiển cạnh xuống CS sau cạnh xuống SK một hoặc một vài xung clock hệ thống pclk.

Thời gian ổn định của dữ liệu trên đường DI trước (tDIS) và sau (tDIH) cạnh lên của SK:

Cả 2 thời gian này tối thiểu phải bằng 400 ns cho trường hợp xấu nhất. Trong thiết kế, để đảm bảo timing này, dữ liệu trên đường DI sẽ được dịch ra bằng cạnh xuống xung SK. Như vậy, dữ liệu sẽ được giữ ổn định trước cạnh lên SK nửa chu kỳ và sau cạnh lên SK nửa chu kỳ.

Thời gian trễ của dữ liệu trên DO là tPD0 và tPD1 trong lệnh READ:

Để đảm bảo lấy mẫu đúng dữ liệu trả về từ EEPROM trên DO, thiết kế sẽ lấy mẫu dữ liệu theo cạnh xuống SK. Ví dụ, trường hợp điện áp EEPROM sử dụng trong tầm rộng từ 1.8V <= VCC <= 5.5V, cả 2 độ trễ này đều là 1000 ns. Nếu sử dụng tần số fSK lớn nhất là 0.25 Mhz thì chu kỳ là 4000 ns, nửa chu kỳ là 2000 ns. Nếu trừ đi độ trễ thì thời gian dữ liệu ổn định trước cạnh xuống SK là 1000 ns và đảm bảo lấy mẫu đúng dữ liệu trên DO.

Thời gian để DO có giá trị bit trạng thái hợp lệ tSV:

Trong chế độ lập trình, ghi hoặc xóa, bit trạng thái chỉ hợp lệ sau khi CS tích cực một khoảng thời gian bằng tSV. Nghĩa là, sau khoảng thời gian này mới được phép kiểm tra giá trị bit trạng thái. Vì DO sẽ được lấy mẫu bằng cạnh xuống SK nên khoảng thời gian từ cạnh lên CS đến cạnh xuống SK đầu tiên là 1 chu kỳ SK. Như vậy, thời điểm lấy mẫu luôn lớn hơn tSV. Ví dụ, trường hợp 1.8V <= VCC <= 5.5V, giá trị lớn nhất của tSV = 1000 ns nhưng 1 chu kỳ SK nhỏ nhất bằng 4000 ns ứng với fSK lớn nhất là 0.25 Mhz nên luôn thỏa mãn yêu cầu.

Thời gian để DO quay về trạng thái tổng trở cao high-Z sau khi CS xuống mức "0" là tDF:

Sau khi CS xuống mức thấp thì phải đợi sau thời gian này để DO trở về trạng thái high-Z trước khi tích cực CS để thực hiện truy xuất tiếp theo. Bên cạnh đó, datasheet cũng quy định thời gian giữa 2 lần truy xuất EEPROM là tCS, tính từ cạnh xuống CS của lần truy xuất trước đến cạnh lên CS của lần truy xuất tiếp theo, nên khoảng thời gian chờ giữa 2 lần truy xuất phải lớn hơn hoặc bằng max(min(tCS), max(tDF)).

Trong thiết kế, một chu kỳ SK sẽ được chọn để làm khoảng cách giữa 2 lần truy xuất bộ nhớ EEPROM.

Sơ đồ timing của thiết kế điều khiển EEPROM sau khi phân tích như hình sau:

Căn cứ trên chức năng của lõi IP, sơ đồ khối có thể được phân chia như sau:

Kết thúc bài 1, chúng ta có thể hình dung được tổng quan về lõi IP sẽ thiết kế. Đồng thời, các đặc điểm về timing tín hiệu cũng được phân tích để thiết kế có thể đáp ứng được yêu cầu của bộ nhớ.

Thiết kế sử dụng clock đồng bộ pclk. Để tạo ra xung SK phù hợp, một thanh ghi sẽ được sử dụng cho phép thiết lập hệ số để chia clock pclk thành xung SK với duty cycle là 50%, nghĩa là độ rộng mức cao và mức thấp trong 1 chu kỳ SK bằng nhau. Bạn có thể chọn duty cycle khác nhưng việc chọn duty cycle 50% giúp cho việc thiết kế bộ chia clock đơn giản hơn.

|

| Hình 10. Minh họa về duty cycle |

Vì chúng ta sẽ thiết kế tạo xung SK có duty cycle là 50% nên chỉ cần chu kỳ fSK thỏa mãn là 2 thông số này thỏa mãn. Ví dụ, ở điều kiện 4.5V <= Vcc <= 5.5V, tần số fSK được thiết lập tối đa là 2 Mhz thì chu kỳ là 500 ns. Vì duty cycle là 50% nên, mỗi chu kỳ SK có 250 ns mức "1" và 250 ns mức "0" và thỏa mãn yêu cầu về độ rộng fSKH và fSKL.

Thời gian giữa cạnh lên CS và cạnh lên đầu tiên của SK (tCSS):

Trường hợp xấu nhất, tCSS tối thiếu bằng 200 ns nên một nửa xung SK sẽ được dùng để tạo độ trễ này. Một nữa xung SK, cho trường hợp nhanh nhất bằng 250ns khi fSK = 2 Mhz sẽ luôn thỏa mãn yêu cầu và giúp thiết kế đơn giản hơn.

Thời gian giữa cạnh xuống xung SK cuối cùng và cạnh xuống của CS (tCSH):

Độ trễ yêu cầu là 0 ns, tức là không cần trễ. Nếu trong thiết kế, chúng ta cho CS xuống cùng với cạnh xuống SK thì cạnh xuống CS tại chân EEPROM có thể xuất hiện trước cạnh xuống xung SK vì độ trễ của SK khi kết nối từ bộ điều khiển đến EEPROM có thể lớn hơn độ trễ của CS. Để tránh điều này, thiết kế sẽ sẽ điều khiển cạnh xuống CS sau cạnh xuống SK một hoặc một vài xung clock hệ thống pclk.

Thời gian ổn định của dữ liệu trên đường DI trước (tDIS) và sau (tDIH) cạnh lên của SK:

Cả 2 thời gian này tối thiểu phải bằng 400 ns cho trường hợp xấu nhất. Trong thiết kế, để đảm bảo timing này, dữ liệu trên đường DI sẽ được dịch ra bằng cạnh xuống xung SK. Như vậy, dữ liệu sẽ được giữ ổn định trước cạnh lên SK nửa chu kỳ và sau cạnh lên SK nửa chu kỳ.

Thời gian trễ của dữ liệu trên DO là tPD0 và tPD1 trong lệnh READ:

Để đảm bảo lấy mẫu đúng dữ liệu trả về từ EEPROM trên DO, thiết kế sẽ lấy mẫu dữ liệu theo cạnh xuống SK. Ví dụ, trường hợp điện áp EEPROM sử dụng trong tầm rộng từ 1.8V <= VCC <= 5.5V, cả 2 độ trễ này đều là 1000 ns. Nếu sử dụng tần số fSK lớn nhất là 0.25 Mhz thì chu kỳ là 4000 ns, nửa chu kỳ là 2000 ns. Nếu trừ đi độ trễ thì thời gian dữ liệu ổn định trước cạnh xuống SK là 1000 ns và đảm bảo lấy mẫu đúng dữ liệu trên DO.

Thời gian để DO có giá trị bit trạng thái hợp lệ tSV:

Trong chế độ lập trình, ghi hoặc xóa, bit trạng thái chỉ hợp lệ sau khi CS tích cực một khoảng thời gian bằng tSV. Nghĩa là, sau khoảng thời gian này mới được phép kiểm tra giá trị bit trạng thái. Vì DO sẽ được lấy mẫu bằng cạnh xuống SK nên khoảng thời gian từ cạnh lên CS đến cạnh xuống SK đầu tiên là 1 chu kỳ SK. Như vậy, thời điểm lấy mẫu luôn lớn hơn tSV. Ví dụ, trường hợp 1.8V <= VCC <= 5.5V, giá trị lớn nhất của tSV = 1000 ns nhưng 1 chu kỳ SK nhỏ nhất bằng 4000 ns ứng với fSK lớn nhất là 0.25 Mhz nên luôn thỏa mãn yêu cầu.

Thời gian để DO quay về trạng thái tổng trở cao high-Z sau khi CS xuống mức "0" là tDF:

Sau khi CS xuống mức thấp thì phải đợi sau thời gian này để DO trở về trạng thái high-Z trước khi tích cực CS để thực hiện truy xuất tiếp theo. Bên cạnh đó, datasheet cũng quy định thời gian giữa 2 lần truy xuất EEPROM là tCS, tính từ cạnh xuống CS của lần truy xuất trước đến cạnh lên CS của lần truy xuất tiếp theo, nên khoảng thời gian chờ giữa 2 lần truy xuất phải lớn hơn hoặc bằng max(min(tCS), max(tDF)).

Trong thiết kế, một chu kỳ SK sẽ được chọn để làm khoảng cách giữa 2 lần truy xuất bộ nhớ EEPROM.

Sơ đồ timing của thiết kế điều khiển EEPROM sau khi phân tích như hình sau:

|

| Hình 11. Sơ đồ timing giao tiếp EEPROM của bộ điều khiển |

- APB_INTF: khối giao tiếp và đáp ứng giao thức APB. Khối này sẽ chứa các thanh ghi cấu hình và trạng thái của lõi IP trong quá trình hoạt động từ đó tạo các tín hiệu điều khiển các khối khác.

- CLOCK_GEN: khối tạo txung SK, tín hiệu dịch bit trên ec_di và tín hiệu lấy mẫu bit trên eeprom_do.

- EEPROM_INTF: khối tạo tín hiệu điều khiển EEPROM

|

| Hình 12. Sơ đồ khối lõi IP điều khiển bộ nhớ EEPROM |