Flip-Flop (FF) và Latch có cấu tạo và hoạt động khác nhau nên việc kiểm tra timing cho FF và Latch có một vài điểm khác biệt. Bài viết này trình bày sự khác nhau trong phân tích timing của FF và Latch. Vì loại FF và Latch được sử dụng phổ biến là loại D nên bài viết này chỉ trình bày về D FF và D Latch.

1) Cấu trúc và hoạt động của FF

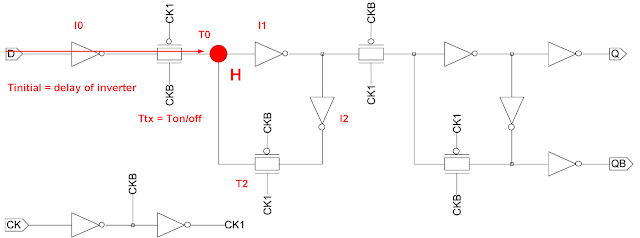

Một D FF thông thường không tích hợp các chức năng như reset/set, scan, ... có sơ đồ mạch nguyên lý (schematic) như hình 1.

|

| Hình 1: Sơ đồ mạch nguyên lý của DFF |

Mạch nguyên lý của FF được biểu diễn bằng các cổng truyền (transmission gate) và các cổng đảo (inverter). Trong đó cổng truyền có cấu trúc gồm một nMOS và pMOS mắc song song như hình 2. Khi CK = 1 (tương ứng CKN = 0), cổng truyền sẽ mở cho dữ liệu truyền từ IN đến OUT, điện trở từ IN đến OUT lúc này rất thấp, khoảng từ 100Ω trở xuống. Khi CK = 0 (tương ứng CKN = 1), cổng truyền sẽ đóng và cổng có trạng thái tổng trở cao (high-Z), khoảng vài MΩ trở lên.

|

| Hình 2: Cấu trúc và bảng sự thật của công truyền |

Hoạt động của D FF được minh họa trong hình 3. Khi clock CK = 0, hai cổng truyền T0 và T3 mở, T1 và T2 đóng. Dữ liệu từ chân D được truyền vào trong tầng thứ nhất của D FF nhưng không truyền tiếp đến tầng thứ 2 vì T1 đóng. Giá trị trên chân Q và QB lúc này được duy trì như cũ nhờ mạch lặp L1.

Khi clock CK chuyển từ giá trị 0 thành giá trị 1, T0 và T3 đi vào trạng thái đóng, T1 và T2 đi vào trạng thái mở. Giá trị từ tầng thứ nhất của D FF được truyền qua tầng thứ 2 của D FF và tác động lên chân Q và QB.

Trong suốt quá trình CK = 1, D không ảnh hưởng đến giá trị ngõ ra của FF nữa vì T0 đóng. Giá trị ngõ ra Q và QB được duy trì bởi mạch lặp L0.

Khi clock CK chuyển từ giá trị 0 thành giá trị 1, T0 và T3 đi vào trạng thái đóng, T1 và T2 đi vào trạng thái mở. Giá trị từ tầng thứ nhất của D FF được truyền qua tầng thứ 2 của D FF và tác động lên chân Q và QB.

Trong suốt quá trình CK = 1, D không ảnh hưởng đến giá trị ngõ ra của FF nữa vì T0 đóng. Giá trị ngõ ra Q và QB được duy trì bởi mạch lặp L0.

|

| Hình 3: Hoạt động của D FF |

Xét khoảng thời gian từ T1 đến T2, giá trị D tại thời điểm CK chuyển từ 0 sang 1 được truyền từ tầng thứ nhất D FF sang tầng thứ 2 của D FF và làm ngõ ra Q bằng 1. Sau đó, nếu D có thay đổi giá trị thì cũng không ảnh hưởng đến Q và T0 đã đóng.

|

| Hình 4: Dạng sóng minh họa hoạt động của D FF |

Xét hình 5, giá trị từ D phải mất một khoảng thời gian để đi qua cổng đảo I0, cồng truyền T0, cồng đảo I1 và cổng đảo I2 trước khi có mặt tại điểm S. Khoảng thời gian này chính là thời gian SETUP (Setup time). D phải đảm bảo đã ổn định trước khoảng thời gian Setup để giá trị tại điểm S ổn định. Giá trị tại S sẽ được giữ bởi mạch lặp I1-I2-T2 khi xuất hiện cạnh lên clock.

|

| Hình 5: Setup time là độ trễ từ D đến điểm Z |

Hình 6 minh họa việc xác định hold time, hold time là khoảng thời gian mà tại đó, ngõ vào D phải giữ ổn định để giá trị tại điểm H đảm bảo ổn định. Hold time là thời gian phụ thuộc vào độ trễ của mạch tổ hợp từ chân D đến cổng truyền T và thời gian đóng của cổng truyền T0 tại cạnh lên xung clock. Cổng truyền cần một khoảng thời gian nhất định để đóng/mở. Khoảng thời gian đó bị ảnh hưởng bởi:

- Độ trễ của hai tín hiệu điều khiển CK1 và CKB

- Độ trễ khi chuyển trạng thái của bản thân cổng truyền

Hold time sẽ được xác định bởi thời gian khởi động (Tinitial) và thời gian cổng truyền đóng hoặc mở (Ttx). Thời gian khởi động là độ trễ của mạch tổ hợp từ chân D đến cổng truyền T0. Trong hình 6, Tinitial là độ trễ trên cổng đảo I0.

|

| Hình 6: Thông số vật lý từ D đến điểm H sẽ xác định hold time của FF |

Đối với các loại D FF khác nhau, độ trễ khởi động sẽ có sự chênh lệch đáng kể vì mạch tổ hợp trên đường từ D đến cổng truyền T0 là khác nhau. Hình 7 minh họa một số mạch tổ hợp trên đường từ D đến T0 của một số loại D FF.

|

| Hình 7: Mạch tổ hợp đầu vào của một số loại D FF. (a) D FF có hỗ trợ chức năng scan (b) D FF có hỗ trợ chân reset đồng bộ |

Xét lại hình 6, để giá trị tại điểm H ổn định thì giá trị tại D phải giữ ổn định trong thời gian cổng truyền T0 đóng. Sự chênh lệch giá trị giữa thời gian khởi động và thời gian đóng/mở của cổng truyền sẽ làm cho hold time có thể mang giá trị âm, bằng 0 hoặc dương.

Nếu Ttx > Tinitial, tức thời gian đóng cổng truyền lớn hơn thời gian khởi động thì hold time gọi là dương. Điều này tương ứng với việc D phải giữ giá trị ổn định sau khi xuất hiện cạnh lên clock một khoảng thời gian. Khoảng thời gian này cộng với Tinitial phải đảm bảo lớn hơn thời gian Ttx để bảo bảo T0 đã đóng.

Nếu Ttx = Tinitial, tức thời gian đóng cổng truyền bằng thời gian khởi động thì hold time bằng 0. Điều này tương ứng với việc D có thể thay đổi giá trị ngay sau khi cạnh lên clock xuất hiện vì độ trễ trên cổng I0 làm cho sự thay đổi tại D đến đầu vào T0 khi nó đã đóng.

Nếu Ttx < Tinitial, tức thời gian đóng cổng truyền nhỏ hơn thời gian khởi động thì hold time gọi là âm. Điều này tương ứng với việc D có thể thay đổi giá trị trước cạnh lên clock một khoảng thời gian.

2) Cấu trúc và hoạt động của Latch

Khác với FF, Latch hoạt động theo mức (level) của tín hiệu clock. Hình 9 là sơ đồ mạch nguyên lý của một D Latch theo các cổng truyền và cổng đảo.

Khi G = 0, CK1 = 0 và CKB = 1, T0 đóng và T1 mở. Giá trị ngõ ra Q và QB của Latch được giữ cố định bởi mạch lặp L1. Khi G = 1, CK1 = 1 và CKB = 0, cổng truyền T0 mở và T1 đóng. Lúc này, giá trị trên chân D đi qua T0 và tác động trực tiếp đến giá trị trên chân Q và QB. Nguyên lý hoạt động này được minh họa trong hình 10.

Latch cũng có quy định về setup time và hold time. Timing của Latch liên quan đến thời điểm chân G chuyển từ mức tích cực sang thôi tích cực, trong ví dụ hình 10 là khi G chuyển từ 1 sang 0. Xét hình 11, D phải ổn định trước khi T0 đóng và T1 mở để giá trị tại điểm S ổn định và D phải giữ giá trị ổn định này một khoảng thời gian để đảm bảo H ổn định trong khi T0 đang đóng.

3) Kiểm tra timing cho FF

Nếu Ttx = Tinitial, tức thời gian đóng cổng truyền bằng thời gian khởi động thì hold time bằng 0. Điều này tương ứng với việc D có thể thay đổi giá trị ngay sau khi cạnh lên clock xuất hiện vì độ trễ trên cổng I0 làm cho sự thay đổi tại D đến đầu vào T0 khi nó đã đóng.

Nếu Ttx < Tinitial, tức thời gian đóng cổng truyền nhỏ hơn thời gian khởi động thì hold time gọi là âm. Điều này tương ứng với việc D có thể thay đổi giá trị trước cạnh lên clock một khoảng thời gian.

|

| Hình 8: Minh họa hold time dương, bằng 0 và âm. Trong cả 3 trường hợp, D không vi phạm setup time và hold time nên ngõ ra Q đều là 1 |

Khác với FF, Latch hoạt động theo mức (level) của tín hiệu clock. Hình 9 là sơ đồ mạch nguyên lý của một D Latch theo các cổng truyền và cổng đảo.

|

| Hình 9: Sơ đồ mạch nguyên lý của D Latch |

|

| Hình 10: Cấu tạo và hoạt động của D Latch |

|

| Hình 11: Setup time and hold time của D Latch |

Phương pháp kiểm tra setup time và hold time cho FF và Latch có sự khác nhau. FF hoạt động theo cạnh clock, mối quan hệ giữa thời gian dữ liệu đến FF trên đường dữ liệu và thời gian xuất hiện cạnh clock trên đường clock phải tuân thủ nghiêm ngặt.

Xét ví dụ hình 12,giả sử FF của một thư viện công nghệ (technology library) có thông số setup time tối thiểu là 2ns và hold time tối thiểu là 1ns. Mặc định, phần mềm kiểm tra timing sẽ kiểm tra timing của một đường dữ liệu trong một chu kỳ xung clock, từ cạnh launch của FF1 đến cạnh capture tại FF2.

Khi kiểm tra setup, phần mềm sẽ kiểm tra dữ liệu sau khi được khởi tạo tại FF1 sẽ đi đến FF2 trong 1 chu kỳ xung clock và ổn định trước cạnh lên xung clock của FF2 là 2ns. Nếu độ trễ đường dữ liệu lớn, dữ liệu đến FF2 không đảm bảo thời gian "trước cạnh clock capture 2ns" thì vi phạm timing xảy ra. Trong kiểm tra timing, phần mềm sẽ luôn xem xét trường hợp xấu nhất để xác định xem timing có vi phạm hay không. Đối với kiểm tra setup, phần mềm kiểm tra sẽ tính toán trên độ trễ lớn nhất trên của đường dữ liệu và độ trễ nhỏ nhất của đường clock giữa FF1 và FF2, đây chính là trường hợp xấu nhất để đánh giá setup time.

4) Kiểm tra timing cho Latch

Thiết kế sử dụng Latch thường dùng các clock 2 pha (two-phase) và không chồng lấp (non-overlapping) để điều khiển các thanh ghi (thanh ghi ở đây là Latch) mắc liền kề nhau trên đường dữ liệu. Các clock two-phase là các clock lệch pha nhau. Các clock non-overlapping là các clock có mức tích cực không chồng cấp nhau.

Ví dụ, xét một thiết kế Latch sử dụng clock two-phase như hình 14, các Latch này có mức tích cực ở chân G là mức cao. L0 và L2 được điều khiển bởi CK0 và L1 được điều khiển bởi CK1. Giả sử setup time của mỗi Latch là 2ns và hold time của mỗi Latch là 1ns.

Việc kiểm tra setup time được thực hiện từ cạnh launch của Latch trước đến cạnh close của Latch kế tiếp. Đối với Latch L1 thì dữ liệu đến chân D phải đảm bảo trước cạnh close 2ns. Chú ý, Latch kiểm tra setup time tại cạnh close chứ không phải tại cạnh open.

Tại L1, tùy vào độ trễ mạch tổ hợp trên đường timing từ L0 đến L1 (path L0.G-L1.D) mà đữ liệu có thể đến trước cạnh open của Latch L1 hoặc sau cạnh open của Latch. Thời điểm này sẽ ảnh hưởng đến việc tính toán và kiểm tra timing của Latch L2.

Nếu dữ liệu truyền từ L0 đến chân D của L1 trước cạnh open của L1 (ví dụ như tại thời điểm a0) thì dữ liệu này sẽ bắt đầu được bắt tại cạnh open của L1. Giống như việc phân tích timing cho FF, việc phân tích timing được thực hiện trên đường từ chân G của L1 đến chân D của L2 (path L1.G-L2.D). Trong trường hợp này, đường timing từ L0 đến L1 không mượn (borrow) thời gian của đường timing từ L1 đến L2.

Nếu dữ liệu truyền đến chân D của L1 sau cạnh open của L1 (ví dụ như tại thời điểm a1). Đường timing từ L1 đến L2 được khởi tạo từ chân D của L1 chứ không từ vị trí cạnh open tại chân G của L1 nữa (path L1.D-L2.D). Trong trường hợp này, đường timing từ L0 đến L1 được nói là "mượn" thời gian của đường timing từ L1 đến L2.

Đối với đường timing từ L0 đến L1, phần mềm phân tích timing sẽ báo cáo giá trị slack như sau:

|

| Hình 12: Kiểm tra timing cho FF |

Khi kiểm tra setup, phần mềm sẽ kiểm tra dữ liệu sau khi được khởi tạo tại FF1 sẽ đi đến FF2 trong 1 chu kỳ xung clock và ổn định trước cạnh lên xung clock của FF2 là 2ns. Nếu độ trễ đường dữ liệu lớn, dữ liệu đến FF2 không đảm bảo thời gian "trước cạnh clock capture 2ns" thì vi phạm timing xảy ra. Trong kiểm tra timing, phần mềm sẽ luôn xem xét trường hợp xấu nhất để xác định xem timing có vi phạm hay không. Đối với kiểm tra setup, phần mềm kiểm tra sẽ tính toán trên độ trễ lớn nhất trên của đường dữ liệu và độ trễ nhỏ nhất của đường clock giữa FF1 và FF2, đây chính là trường hợp xấu nhất để đánh giá setup time.

- Độ lớn nhất trên đường dữ liệu là thời gian dài nhất mà dữ liệu đi từ FF1 đến FF2, tính từ cạnh launch ở FF1 đến chân D của FF2

- Độ trễ ngắn nhất của đường clock giữa FF1 và FF2 làm cho thời gian giữa cạnh lauch của chu kỳ hiện tại và cạnh capture của chu kỳ hiện tại là ngắn nhất.

- Độ trễ nhỏ nhất của đường dữ liệu là thời gian ngắn nhất mà dữ liệu đi từ FF1 đến FF2

- Độ trễ lớn nhất của đường clock giữa FF1 và FF2 làm cho thời gian giữa cạnh launch của chu kỳ hiện tại và cạnh capture của chu kỳ clock trước đó là dài nhất.

4) Kiểm tra timing cho Latch

Thiết kế sử dụng Latch thường dùng các clock 2 pha (two-phase) và không chồng lấp (non-overlapping) để điều khiển các thanh ghi (thanh ghi ở đây là Latch) mắc liền kề nhau trên đường dữ liệu. Các clock two-phase là các clock lệch pha nhau. Các clock non-overlapping là các clock có mức tích cực không chồng cấp nhau.

|

| Hình 13: Clock two-phase overlapping (a) và non-overlapping (b) |

|

| Hình 14: Kiểm tra setup time và hold time cho D Latch |

Tại L1, tùy vào độ trễ mạch tổ hợp trên đường timing từ L0 đến L1 (path L0.G-L1.D) mà đữ liệu có thể đến trước cạnh open của Latch L1 hoặc sau cạnh open của Latch. Thời điểm này sẽ ảnh hưởng đến việc tính toán và kiểm tra timing của Latch L2.

Nếu dữ liệu truyền từ L0 đến chân D của L1 trước cạnh open của L1 (ví dụ như tại thời điểm a0) thì dữ liệu này sẽ bắt đầu được bắt tại cạnh open của L1. Giống như việc phân tích timing cho FF, việc phân tích timing được thực hiện trên đường từ chân G của L1 đến chân D của L2 (path L1.G-L2.D). Trong trường hợp này, đường timing từ L0 đến L1 không mượn (borrow) thời gian của đường timing từ L1 đến L2.

Nếu dữ liệu truyền đến chân D của L1 sau cạnh open của L1 (ví dụ như tại thời điểm a1). Đường timing từ L1 đến L2 được khởi tạo từ chân D của L1 chứ không từ vị trí cạnh open tại chân G của L1 nữa (path L1.D-L2.D). Trong trường hợp này, đường timing từ L0 đến L1 được nói là "mượn" thời gian của đường timing từ L1 đến L2.

Đối với đường timing từ L0 đến L1, phần mềm phân tích timing sẽ báo cáo giá trị slack như sau:

- Slack là dương nếu dữ liệu đến L1 trước cạnh open

- Slack là 0 nếu dữ liệu đến sau cạnh open và trước setup time, tương ứng với việc xuất hiện hiện tượng "mượn thời gian" (time borrowing)

- Slack là âm nếu dữ liệu đến vi phạm setup time.

0 bình luận:

Đăng nhận xét