Bài viết này trình bày về việc tính toán độ trễ (delay) và khái niệm về độ trễ ngõ vào, độ trễ ngõ ra trong phân tích timing. Đồng thời minh họa một báo cáo timing (timing report) cơ bản.

Trước khi tham khảo bài này, các bạn nên đọc qua một số bài viết sau đây:

Trước khi tham khảo bài này, các bạn nên đọc qua một số bài viết sau đây:

1) Độ trễ ngõ vào (Input delay)

Trong phân tich timing, việc tính toán giá trị slack dựa trên thông số của phần tử tuần tự, độ trễ giữa startpoint và endpoint, khoảng cách giữa cạnh launch và cạnh capture. Các ví dụ và nội dung trình bày trong bài này dành cho đường Max - setup time.

slack = required time - arrival time (dành cho setup time)

|

| Hình 1: Cách xác định slack |

Đối với một thiết kế, slack của đường dữ liệu từ một linh kiện tuần tự này, ví dụ như FF, đến một linh kiện tuần tự khác có thể xác định dễ dàng vì các thông số cần thiết có đầy đủ.

|

| Hình 2: Các loại đường dữ liệu (data path) |

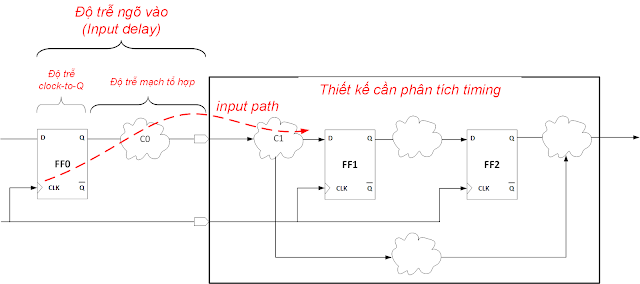

Nhưng đối với loại đường dữ liệu từ ngõ vào (input) của thiết kế đến một linh kiện tuần tự hoặc đến ngõ ra thiết kế, thời gian đến (arrival time) của dữ liệu không thể xác định được từ netlist của thiết kế vì điểm launch nằm ngoài thiết kế. Khi điểm launch nằm ngoài thiết kế, độ trễ bên ngoài, từ một linh kiện tuần tự bên ngoài đến chân ngõ vào thiết kế không thể xác định được nên thời gian dữ liệu xuất hiện tại ngõ vào thiết kế cũng không xác định được. Để phân tích đường timing từ ngõ vào một thiết kế, chúng ta cần mô tả điều kiện timing của logic bên ngoài kết nối với ngõ vào. Điều kiện timing này gọi là độ trễ ngõ vào (input delay).

Trong minh họa hình 3, thiết kế cần phân tích timing có ngõ vào được lái từ FF0, dùng chung clock với FF1, qua mạch tổ hợp rồi đến FF1.D. Độ trễ ngõ vào được tính như sau:

|

| Hình 3: Độ trễ ngõ vào (input delay) |

Độ trễ ngõ vào = độ trễ clock-to-Q của FF0 + độ trễ mạch tổ hợp C0

2) Độ trễ ngõ ra (output delay)

Tương tự, đối với đường dữ liệu có endpoint là ngõ ra thì thời điểm capture nằm ngoài thiết kế nên độ trễ từ chân ngõ ra đến linh kiện tuần tự dùng để bắt dữ liệu ngõ ra này là không thể xác định. Vì vậy, để phân tích timing đường này, chúng ta cần đặc tả điều kiện timing của đường kết nối đến ngõ ra thiết kế. Thông số này gọi là độ trễ ngõ ra (output delay).

Trong ví dụ hình 4, độ trễ ngõ ra được tính như sau:

Trước khi tìm hiểu việc tính toán độ trễ trong phân tích timing tĩnh, chúng ta hãy phân tích và hiểu một báo cáo timing (timing report).

Hình 5 là một báo cáo timing điển hình của các phần mềm phân tích timing (PrimeTime) và tổng hợp (Design Compiler). Báo cáo này thể hiện nhưng giá trị phân tích cho một đường timing từ điểm startpoint modem/qr_tmp với cạnh launch là cạnh lên clock Sysclk|altpll|clk[2] đến điểm endpoint modem/qr với cạnh capture là cạnh lên clock Sysclk|altpll|clk[2]. Loại phân tích timing là loại setup ứng với ký hiệu "max" (ký hiệu "min" là loại kiểm tra timing hold). Báo cáo timing có 3 cột là Point, Incr và Path.

Cột "Point" liệt kê tất cả các điểm mà đường timing đi qua từ startpoint đến endpoint và các độ trễ cộng thêm. Mỗi điểm là chân của một cell, trong ví dụ này, từ startpoint đến endpoint sẽ đi qua các điểm sau:

Cột "Incr" là giá trị được thêm vào (dương) hoặc trừ đi (âm) trong việc tính tổng độ trễ trên đường timing.

Cột "Path" là giá trị cộng dồn tại mỗi điểm. Giá trị cộng dồn tại một điểm lấy từ giá trị ngay trên nó cộng với giá trị cột "Incr" ở vị trí tương ứng. Ví dụ, độ trễ cộng dồn tại điểm lcell_comb6052/OUT (BUF_D6) là:

Phân cuối báo cáo timing, giá trị slack được tính trên thời gian yêu cầu dữ liệu và thời gian đến:

Quá báo cáo timing trên, chúng ta có thể hình dung được các thông số cần thiết để tính toán các giá trị timing.

Giá trị slack được tính thông qua các thông số sau:

Xem hình 6, xét đoạn dây từ buffer qr_tmp_ASTfhInst7779 đến buffer lcell_comb6052 thì qr_tmp_ASTfhInst7779 là cell lái, lcell_comb6052 là cell bị lái.

Trước khi "place and route" (quá trình sắp đặt các khối thiết kế, các cell và đi dây để kết nối các thành phần) độ trễ đường dây chỉ là một giá trị ước lượng của phần mềm phân tích timing. Sau khi "place and route", các thông số RC của đường dây sẽ được lấy chính xác từ độ dài đường dây và vật liệu đường dây.

Tham khảo:

Altera Corporation, AN 554: How to Read HardCopy PrimeTime Timing Reports, Mar.2010

Lịch sử cập nhật:

Tương tự, đối với đường dữ liệu có endpoint là ngõ ra thì thời điểm capture nằm ngoài thiết kế nên độ trễ từ chân ngõ ra đến linh kiện tuần tự dùng để bắt dữ liệu ngõ ra này là không thể xác định. Vì vậy, để phân tích timing đường này, chúng ta cần đặc tả điều kiện timing của đường kết nối đến ngõ ra thiết kế. Thông số này gọi là độ trễ ngõ ra (output delay).

|

| Hình 4: Độ trễ ngõ ra (output delay) |

Độ trễ ngõ ra = Độ trễ mạch tổ hợp C0 + thời gian setup của FF0

3) Tính toán độ trễ trong STATrước khi tìm hiểu việc tính toán độ trễ trong phân tích timing tĩnh, chúng ta hãy phân tích và hiểu một báo cáo timing (timing report).

| |

|

Cột "Point" liệt kê tất cả các điểm mà đường timing đi qua từ startpoint đến endpoint và các độ trễ cộng thêm. Mỗi điểm là chân của một cell, trong ví dụ này, từ startpoint đến endpoint sẽ đi qua các điểm sau:

- Chân clock của cell FF tên modem/qr_tmp

- Chân Q của cell FF tên modem/qr_tmp

- Ngõ ra cell buffer tên modem/qr_tmp_ASTfhInst7779

- Ngõ ra cell buffer tên lcell_comb6052

- Chân D của cell FF tên modem/qr

Cột "Incr" là giá trị được thêm vào (dương) hoặc trừ đi (âm) trong việc tính tổng độ trễ trên đường timing.

Cột "Path" là giá trị cộng dồn tại mỗi điểm. Giá trị cộng dồn tại một điểm lấy từ giá trị ngay trên nó cộng với giá trị cột "Incr" ở vị trí tương ứng. Ví dụ, độ trễ cộng dồn tại điểm lcell_comb6052/OUT (BUF_D6) là:

0.589 = 0.423 (giá trị điểm trước) + 0.166 (giá trị tăng thêm)

Báo cáo timing này có hai phần, nữa phần đầu tính toán thời gian trễ trên đường timing và cho biết thời gian đến trên đường dữ liệu (data arrival time) là 0.614. Phần sau cho biết thời gian yêu cầu phải có dữ liệu được tính từ lúc cạnh lên capture xuất hiện tại điểm định nghĩa clock cộng độ trễ trên đường clock có trừ đi setup time của FF bắt dữ liệu. Thời gian yêu cầu (data riquired time) là 6.334.Phân cuối báo cáo timing, giá trị slack được tính trên thời gian yêu cầu dữ liệu và thời gian đến:

slack = thời gian yêu cầu - thời gian đến = 6.334 - 0.614 = 5.720

|

| Hình 6: Minh họa đường timing trong ví dụ 5 |

Giá trị slack được tính thông qua các thông số sau:

- Thời gian đến của cạnh clock launch tính từ nguồn clock đến chân ngõ vào của lauch FF, tương ứng với điểm qr_tmp.CLK trong hình minh họa 6

- Thời gian đến của cạnh clock capture tình từ nguồn clock đến chân ngõ vào của capture FF, tương ứng với điểm qr.CLK trong hình minh họa 6

- Độ trễ từ startpoint đến endpoint trên đường timing. Trong minh họa hình 6 là độ trễ tổng cộng từ qr_tmp.CLK đến qr.D

- Độ lệch (uncertainty) xấu nhất giữa hai tín hiệu clock

Độ trễ tích lũy (cumulative delay) dọc theo đường timing được tính dựa trên:

- Độ trễ của các cell, thông số này lấy từ thư viện công nghệ dùng để tổng hợp. Trong ví dụ hình 5, các độ trễ của cell gồm độ trễ clock-to-Q của FF qr_tmp, độ trên của các buffer, setup time của FF qr.

- Độ trễ của đường dây kết nối (interconnect delay). Độ trễ này được tính dựa trên các thông số sau:

- Thông số cell lái đường dây

- Thông số tải của cell bị lái bởi đường dây

- Thông số về điện trở và tụ điện của đường dây. Thông số này phụ thuộc đặc tính vật lý, độ dài của đường dây nên chỉ được xác định chính xác sau khi thiết kế đã được layout hoàn chỉnh.

Trước khi "place and route" (quá trình sắp đặt các khối thiết kế, các cell và đi dây để kết nối các thành phần) độ trễ đường dây chỉ là một giá trị ước lượng của phần mềm phân tích timing. Sau khi "place and route", các thông số RC của đường dây sẽ được lấy chính xác từ độ dài đường dây và vật liệu đường dây.

Tham khảo:

Altera Corporation, AN 554: How to Read HardCopy PrimeTime Timing Reports, Mar.2010

Lịch sử cập nhật:

1/ Thêm chú thích đầu bài để chỉ rõ các phân tích và ví dụ trong bài này là dành cho setup time (xem comment 1) - Oct.24.2020