Bài này cố gắng trình bày một cách hiểu chi tiết về khái niệm SoC và cấu trúc cơ bản của một SoC qua đó các đặc điểm ưu việt và bất lợi của SoC cũng sẽ được trình bày.

1) SoC nghĩa là gì?

Khái niệm SoC ngày nay đã trở nên phổ biến. SoC là từ viết tắt của System on a Chip hoặc System on Chip, được hiểu là toàn bộ "một hệ thống" được đóng gói hoàn chỉnh trong một chip (vi mạch điện tử). Một system thông thường là một hệ thống hoàn chỉnh thực hiện một hoặc nhiều chức năng nào đó, ví dụ như một máy tính cá nhân gồm một bo mạch chủ để kết nối các thành phần như CPU, USB, VGA, RS232,...

|

| Hình 1: Minh họa một System (nguồn: http://www.ugurdag.com) |

Một hệ thống như mô tả có nhược điểm là kích thước lớn và tiêu tốn nhiều năng lượng khi hoạt động trong khi nhu cầu về các thiết bị di động, thiết bị dùng PIN, tiết kiệm năng lượng, kích thước nhỏ gọn và giảm chi phí sản phẩm ngày càng tăng. Bên cạnh đó, nhu cầu về đa chức năng, nhiều tiện ích của khách hàng ngày càng cao. Một hệ thống truyền thống sử dụng các chip có khả năng tích hợp thấp, ít chức năng khó đáp ứng nhu cầu khách hàng và nếu đáp ứn được thì giá thành sản phẩm có thể cao do sử dụng nhiều linh kiện hơn, bo mạch phức tạp và lớn hơn, sản phẩn to hơn. Ví dụ, trước đây, điện thoại chỉ có chức năng nghe, gọi, nhắn tin; sau đó thêm chức năng lưu và phát nhạc; sau đó là chụp ảnh; sau đó là kết nối internet, chạy ứng dụng, chơi game; và hiện nay điện thoại không khác gì một máy tính nhỏ.

|

| Hình 2: Nhu cầu về một sản phẩm đa chức năng tăng cao |

Để đáp ứng nhu cầu ngày càng tăng về tiện ích của sản phẩm, một chip ngày càng tích hợp nhiều chức năng hơn và tạo ra khái niệm System on Chip. Ví dụ như chip SoC dưới đây tích hợp một lõi CPU ARM và các ngoại vi như SegLCD, UDB, SCB, UART, CAN, SPI, ...

|

| Hình 3: Một chip SoC sử dụng lõi CPU ARM (nguồn: www.thegeniusworks.com) |

Thực tế, không có tiêu chuẩn chính xác để đánh giá một chip như thế nào thì được xem là SoC nên có SoC chỉ tích hợp một vài ngoại vi,SoC khác thì tích hợp số lượng ngoại vi khổng lồ.

|

| Hình 4: Chip R-Car E2 của Renesas tích hợp nhiều lõi CPU, Video, Audio, DSP, .... (nguồn: en.wikichip.org) |

2) Ưu nhược điểm của SoC?

Ưu điểm của SoC:

- Sử dụng cho các thiết bị điện tử cần kích thước nhỏ như điện thoại, tablet,...

- SoC có mật độ tích hợp cao, nhiều chức năng nên việc làm phần cứng sản phẩm đơn giản hơn, dễ sản xuất hơn, chi phí thấp hơn, thời gian thiết kế sản phẩm nhanh hơn. Sản xuất số lượng đủ lớn, giá thành sẽ giảm đáng kể.

- Sản phẩm sử dụng SoC tiết kiệm năng lượng hơn so với sản phẩm cùng chức năng nhưng không dùng SoC vì số lượng linh kiện lớn hơn, bo mạch làm phức tạp hơn. Khi sản phẩn càng nhiều chức năng thì đặc điểm này càng thấy rõ.

Nhược điểm của SoC: một nhược điểm của SoC là một loại SoC khó đáp ứng nhu cầu của nhiều loại sản phẩm khác nhau. Chính vì vậy, mỗi hãng thiết kế và sản xuất chip đều có nhiều dòng SoC khác nhau, mỗi dòng sẽ đáp ứng một phân khúc sản phẩm nhất định và tối ưu nhất cho phân khúc sản phẩm này. Tối ưu ở đây được hiểu là số lượng chức năng mà chip tích hợp là vừa đủ, không quá nhiều và cũng không quá ít. Quá nhiều chức năng thì giá chip sẽ tăng, giá sản phẩm tăng trong khi chức năng thừa không được dùng đến. Quá ít chức năng thì không đáp ứng được nhu cầu ứng dụng của sản phẩm hoặc làm sản phẩm khó, thời gian ra thị trường lâu.

|

| Hình 5: Mỗi dòng chip SoC sẽ đáp ứng cho một phần khúc sản phẩm (nhu cầu ứng dụng) khác nhau (nguồn: www.renesas.com) |

3) Cấu trúc phần cứng của một SoC?

Như đã trình bày, mỗi chip SoC có mật độ tích hợp chức năng khác nhau nhưng hầu hết các SoC đều có các thành phần cơ bản sau đây:

CPU (Central Processing Unit): Lõi vi xử lý là thành phần không thể thiếu trong một SoC làm nhiệm vụ quản lý toàn bộ hoạt động chính của một SoC. CPU đảm nhiệm luồng xử lý chính trong SoC, điều phối các hoạt động giữa các thành phần khác trong SoC, thực thi các tính toán chính. Một SoC có thể có một hoặc nhiều lõi CPU. Một số lõi CPU:

- Lõi CPU ARM dùng tập lệnh ARM và là sản phẩm của hãng ARM

- RISC-V là các lõi CPU phát triển trên tập lệnh mở và miễn phí RISC-V (riscv.org)

- SH (SuperH) dùng tập lệnh RISC được triển bởi Hitachi và nay là sản phẩm của Renesas

Bus hệ thống (System BUS): Bus hệ thống là có nhiệm vụ kết nối thông suốt các thành phần chức năng khác nhau trong vi xử lý. Bus hệ thống giống như những con đường để vận chuyển dữ liệu giữa các thành phần trong SoC. Một số cấu trúc bus hệ thống:

- AMBA (AXI, AHB, APB) là chuẩn bus phát triển bởi ARM

- CoreConnect là chuẩn bus phát triển bởi IBM

- Avalon là chuẩn bus phát triển bởi Altera, hiện nay đã thuộc Intel

- STBus là chuẩn bus phát triển bởi STMicroelectronic

- Wishbone là chuẩn bus phát triển bởi Silicore Corporation, hiện nay đã được công bố miễn phí trên OpenCores

Bộ nhớ (Memory): Bộ nhớ trong một SoC gọi là bộ nhớ nội để phân biệt với bộ nhớ nằm ngoài SoC và giao tiếp với SoC thông qua các chân (pin) điều khiển của SoC. Bộ nhớ nội này có thể là:

- ROM: lưu cấu hình hoặc chương trình ban đầu của SoC

- RAM: được sử dụng để lưu thông tin hoặc giá trị tính toán trong suốt quá trình hoạt động của SoC

Thành phần điều khiển nội (Internal block): là thành phần chỉ điều khiển hoạt động bên trong SoC mà không điều khiển trực tiếp port nào của SoC như:

- Khối tạo clock (clock generator): Cung cấp clock cho toàn bộ các khối chức năng trong SoC, kể cả CPU

- Khối tạo Reset (reset generator): Cung cấp reset cho toàn bộ các khối chức năng trong SoC, kể cả CPU

- Khối quản lý năng lượng (power management): Điều khiển cấp nguồn (bật/tắt) cho các khối chức năng trong SoC

- Các khối giám sát (Monitor) là các khối có chức năng giám sát hoạt động của SoC, kịp thời phát hiện ra các lỗi trong quá trình hoạt động để khởi động lại một phần hoặc toàn bộ hệ thống.

Ngoại vi (Peripheral): là các khối có thể lái trực tiếp các chân (pin hoặc port) của SoC để thực thi một chức năng điều khiển bên ngoài SoC, ví dụ như:

- UART: truyền nhận dữ liệu nối tiếp bất đồng bộ

- SegLCD: Điều khiển hiện thị trên segment LCD

- Video: Điều khiển camera

- Audio: Thu phát âm thanh

- ADC: bộ chuyển đổi tín hiệu tương tự thành tín hiệu số

- ....

|

| Hình 6: Mô hình minh họa các thành phần cơ bản của một SoC |

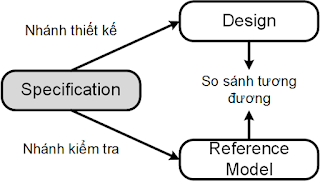

4) Làm sao để xây dựng một SoC

Chúng ta giả sử đã có tất cả các khối chức năng cần thiết như CPU, các ngoại vi, bus hệ thống, ... Để xây dựng một SoC, chúng ta cần làm các công việc cơ bản sau:

|

| Hình 7: Các bước cơ bản để thiết kế một chip SoC |

1) Phân tích cấu trúc SoC: phân tích cấu trúc SoC là trả lời một số cấu hỏi cơ bản sau đây:

- Cấu trúc bus hệ thống của SoC như thế nào?

- Khối chức năng này (CPU, ngoại vi,...) được kết nối đến bus nào?

Ở bước này, chúng ta cần xác định bus hệ thống sẽ bao gồm những bus nào và kết nối với nhau ra sao. Để xác định được cấu trúc bus hệ thống, căn cứ vào phạm vi ứng dụng các master và slave sẽ được lựa chọn. Các thông tin cơ bản về các master và slave sẽ có trong SoC sẽ được liệt kê:

- Chức năng và phạm vi ứng dụng

- Độ rộng đường dữ liệu và địa chỉ

- Tần số hoạt động

Đầu tiên, căn cứ vào phạm vi ứng dụng mà SoC nhắm đến (ứng dụng hiển thị hình ảnh, phân tích dữ liệu, điều khiển tự động, ...) để phân nhóm các Master và slave theo mức độ ưu tiên khác nhau. Ví dụ, chúng ta cần xây dựng một SoC chuyên dùng cho lấy mẫu phân tích dữ liệu cảm biến thời gian thực thì nhóm ưu tiên số 1 phải là các các ngoại vi liên quan đến chức năng này như ADC (dùng để chuyển đổi tín hiệu tương tự từ các cảm biến sang tín hiệu số). Như vậy, nó cần được bố trí ở sao cho việc trao đổi dữ liệu từ ADC đến các master là nhanh nhất.

Căn cứ tiếp theo là dựa vào tốc độ xử lý hoặc tần số hoạt động của các master và slave. Các thành phần tốc độ cao cần được gắn vào các bus có tốc độ cao, các thành phần tốc độ thấp sẽ gắn vào bus tốc độ thấp tương ứng.

Căn cứ trên độ rộng bus dữ liệu để gắn master và slave đến bus có độ rộng bus dữ liệu phù hợp.

Sau khi kết thúc bước này, chúng ta sẽ có được cấu trúc SoC như hình 6 và mô tả về giao tiếp của các bus thể hiện tần số bus; số lượng master, slave; độ rộng đường dữ liệu,...

|

| Hình 8: Cấu trúc của STM32L151x6/8/B hãng ST |

Trong ví dụ hình 8, hệ thống gồm 1 bus AHB và 2 bus APB đều có tần số tối đa là 32 Mhz.

2) Phân tích chi tiết

2) Phân tích chi tiết

Trong bước này, chúng ta cần phân tích rõ các vấn đề sau:

- Một master có thể truy xuất đến những slave nào và qua những bus nào?

- Một slave có thể được truy xuất bởi những master nào và thông qua những bus nào?

- Vùng địa chỉ của mỗi slave là bao nhiêu? từ địa chỉ nào đến địa chỉ nào?

|

| Hình 9: Ví dụ về phân vùng địa chỉ cho mỗi slave trong hệ thống SoC |

3) Kết nối hệ thống

Thực hiện kết nối các master, slave đến các bus như đã phân tích.

4) Kiểm tra kết nối

Thực hiện kiểm tra lỗi cú pháp bằng các phần mềm chuyên dụng như Leda, Spyglass để đảm bảo các kết nối là đúng. Nếu việc kết nối này được thưng hiện thông qua một phần mềm chuyên dụng để xây dựng SoC thì các kết nối thường đã được kiểm tra và cảnh báo trong quá trình xây dựng SoC.

5) Kiểm tra chức năng

Thực hiện mô phỏng mức hệ thống để đảm bảo tất cả các master đều có thể truy cập đến các slave của nó trong vùng địa chỉ đã quy định. Nếu truy cập ngoài vùng địa chỉ quy định thì hệ thống vẫn hoạt động thông suốt nhưng sẽ có cơ chế cảnh báo.

Chú ý, bước này không phải là mô phỏng chức năng các thành phần trong hệ thống như kiểm tra chức năng khối video, khối UART hay bất kỳ khối nào khác mà chỉ kiểm tra tính thông suốt của hệ thống SoC đã xây dựng.

6) Kiểm tra hiệu năng

Thực hiện mô phỏng kiểm tra để đảm bảo băng thông truy xuất của các master đến các slave hoặc bộ nhớ đáp ứng yêu cầu đặt ra. Việc truy xuất của các master, nhất là các master được ưu tiên phải đảm bảo được hoàn thành trong một khoảng thời gian cho phép. Nếu không đạt được thì SoC sẽ không đáp ứng được hiệu năng mong muốn. Ví dụ, master DSP luôn phải được đảm bảo một băng thông đọc bộ nhớ là 10 Mbps (đây chỉ là ví dụ minh họa, không có ý nghĩa áp dụng thực tế) để kịp tính toán và đưa ra kết quả kịp thời thì dù cho toàn bộ các master trong SoC đang truy xuất đến bộ nhớ thì hệ thống SoC vẫn phải đảm bảo bằng thông 10 Mbps cho master DSP.